หลังจากที่เปลี่ยน CEO ใหม่มาได้สักพัก ดูเหมือนอินเทลจะจริงจังกับการให้ความสำคัญของการผลิตชิปประมวลผลมากขึ้น ล่าสุดทางอินเทลภูมิใจประกาศว่า ขณะนี้พวกเขาออกแบบโหนด 2.0 และ 1.8 นาโนเมตรเสร็จแล้ว เตรียมพร้อมสู่การผลิตครับ

ปัจจุบันเทคโนโลยีการผลิตชิปของอินเทล สามารถทำได้ถึงขนาด 3 นาโนเมตร โดยยังอยู่ในขั้นตอนของการทดสอบต่าง ๆ ก่อนที่จะนำมาใช้ในซีพียูระดับ Consumer ภายในช่วงปีหน้า ซึ่งในระหว่างนั้นก็ได้มีการออกแบบโครงสร้างของชิปในยุคอังสตรอมไปด้วย

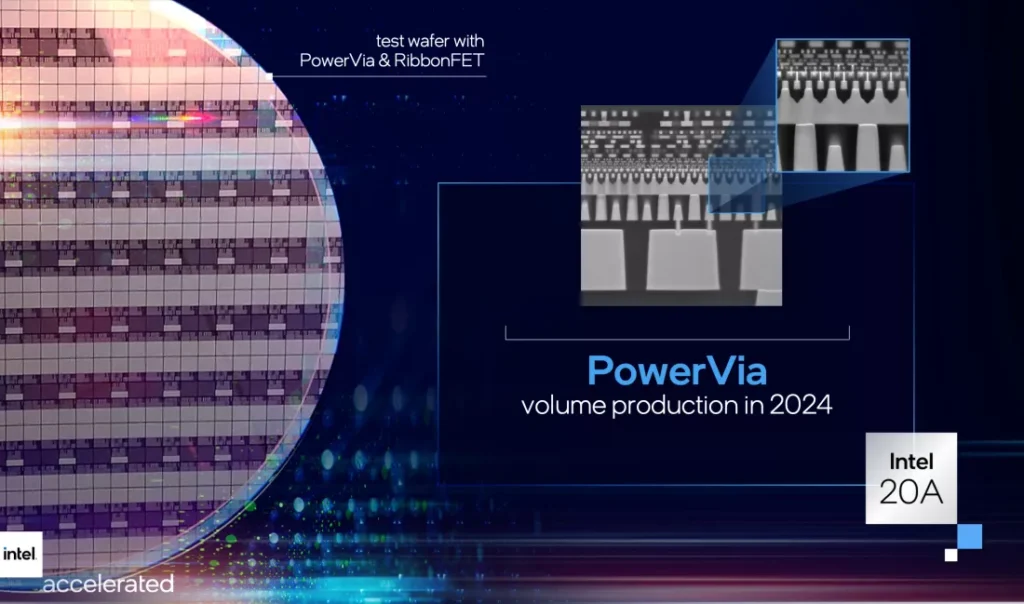

เทคโนโลยีที่ใช้ในการผลิตโหนดขนาดเล็กแบบนี้เรียกว่า gate-all-around FET transistors (GAAFET) ซึ่งจะนิยมใช้ในกรณีที่ระยะของ Transistor gate น้อยกว่า 3 นาโนเมตร ซึ่งอินเทลก็มีชื่อเรียกให้กับมันว่า RibbonFET (จริง ๆ นำเสนอไว้ตั้งแต่ปี 2011 แล้วล่ะ)

จุดเด่นของ RibbonFET คือ PowerVia สามารถเพิ่มความหนาแน่นและความเร็วของชิปได้ ในขณะที่พลังงานรั่วไหลจะน้อยกว่า แน่นอนว่าประสิทธิภาพดีกว่าคู่แข่งอย่าง TSMC และ Samsung ด้วย

อย่างไรก็ตาม แม้จะออกแบบเสร็จแล้ว แต่ความรวดเร็วในการผลิตจะขึ้นอยู่กับปัจจัยอื่นด้วย เพราะการผลิตโหนดที่เล็กขนาดนี้อินเทลจะต้องใช้เครื่อง Twinscan EXE scanners หัวขนาด 0.55 NA optics จาก ASML ซึ่งถ้ายังไม่ได้ใช้ก็จะไม่สามารถผลิตโหนดนี้ได้

เดี๋ยวคงต้องมารอดูว่าพอถึงยุคอังสตรอม (1A = 0.1 นาโนเมตร) อินเทลจะแรงโหดจัดขนาดไหน แล้วทางค่ายแดงจะแก้เกมยังไง ไว้รอติดตามชมกันครับ

ขอขอบคุณข้อมูลจาก Techspot

You must be logged in to post a comment.