TSMC 5nm Process Offers Decent Improvements

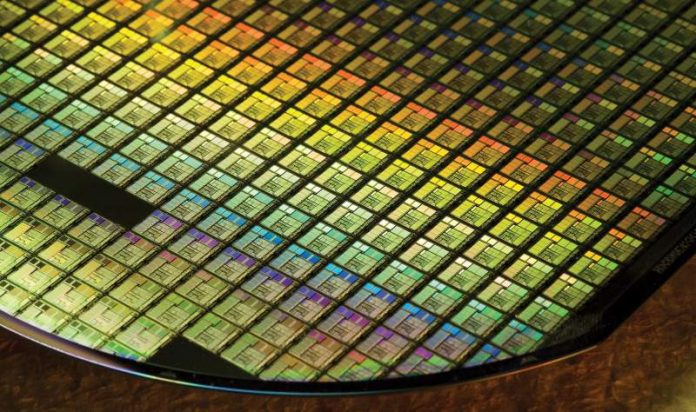

คงจะอีกไม่กี่ปีข้างหน้าแล้วที่ตัว silicon จะไม่ใช่มีไว้เพื่อในการผลิตชิป. เหตุเพราะกระบวนการผลิต nodes เริ่มที่จะมีขนาดที่เล็กลงๆเข้าไปทุกทีและมีความยากมากขึ้นที่จะเล็กลงไปเรื่อยๆ. แต่ ณ ตอนนี้มันยังมีที่เหลือให้กระทำอยู่สำหรับ process nodes ใหม่ๆ. ปีหน้าเราจะเห็นกระบวนการผลิตรูปแบบ 7nm สำหรับตัวชิป. แน่นอนว่าหลังจากนั้นเราจะได้เห็นรูปแบบ 5nm. คาดว่าน่าจะเป็นปี 2020, ทาง TSMC ออกมาเปิดเผยรายละเอียด/details สำหรับกระบวนการผลิตให้เข้าใจมากยิ่งขึ้น.

เพื่อให้บรรลุถึงสายพานการผลิตรูปแบบ 5nm, ทาง TSMC เปลี่ยนมาใช้ EUV หรือ Extreme Ultraviolet/รังสีในการพิมพ์ผัง. EUV จะเป็นอีกวิธีหนี่งที่จะสามารถผลิต nodes ให้เล็กลงไปได้อีก. และเนื่องจากกรรมวิธีในการใช้ EUV ที่ไม่งาย, ทาง TSMC จะเริ่มใช้กับ 7nm เจนที่สองก่อน. ด้วยวิธีนี้จะทำให้ความหนาแน่นนั้นออกมาได้ดีมากยิ่งขึ้นถึง 17% (พื้นที่) และเกิดความชำนาญ. ผลที่ได้ก็จะเกิดประโยชน์อย่างยิ่งกับรูปแบบ 5nm.

TSMC จะนำเสนอพลังงานรูปแบบใหม่มาใช้กับ 5nm

เนื่องจาก EUV มีศักยภาพในการผลิต node ได้เล็กลงกว่าเดิม, รูปแบบ 5nm จะสามารถเพิ่มความหนาแน่นได้มากกว่าเดิมถึง 45%. แต่หากถามถึงทางด้านประสิทธิภาพของพลังงาน, อันนี้จะดีขึ้นเพียงแค่ 20% และทางด้านประสิทธิภาพแค่ 15% หากเทียบกับ 7nm. ซึ่งเทียบกับเงินที่ลงไป, ถือว่าสิ่งที่ได้กลับมานั้นน้อยนิด. สิ่งที่น่าสนใจก็คือจะมีการนำเอา Extremely Low Threshold Voltage/แรงดันไฟรูปแบบใหม่มาใช้, ซึ่งจะทำให้ตัวชิปนั้นสามารถทำ frequency boost ได้ดีมากขึ้นถึง 25% (รายละเอียดยังไม่เปิดเผย).

อย่างที่เคยเกริ่นเอาไว้เมื่อเร็วๆนี้, ทาง TSMC ได้ปรับปรุง fab/สถานีวิจัยและพัฒนาขึ้นมาใหม่ เพื่่อมารองรับสายพานการผลิตรูปแบบ 5nm. สำหรับ fab 18 ใหม่นี้, แน่นอนว่าตัวพระเอกก็คือ EUV ซึ่งจะถูกมาลำเรียงในสายพานการผลิต. ณ ตอนนี้, EUV ยังไม่พร้อมที่จะขึ้นแท่นเพื่่อผลิตรูปแบบสายพานการผลิตรูปแบบอุตสาหกรรม, แต่่ก็ใกล้แล้ว. ส่วนรูปแบบ 7nm ก็จะเริ่มเดินสายพานได้/production ภายในสิ้นปีนี้, และสำหรับ 7nm+ ก็จะเริ่มกันในปี 2019 และ 5nm ในปี 2020. แน่นอนว่าในอนาคตอีก 10 ปีข้างหน้า, เราจะยังเห็น silicon อยู่หรือไม่่. แต่่ทาง TSMC มีแผนที่จะพัฒนารูปแบบ 3nm กันแล้ว.

ที่มาเครดิต/Sources: