ในการผลิตชิปประมวลผล จะมีส่วนประกอบหนึ่งที่เป็นส่วนสำคัญในการประมวลผลของชิป นั่นคือ SRAM หรือที่เรารู้จักกันในชื่อของ แคช (Cache) ซึ่งทำหน้าที่เก็บข้อมูลสำคัญ ๆ ที่ถูกเรียกใช้บ่อยเพื่อติดต่อกับแกนประมวลผลได้โดยตรง แถมยังมีความเร็วมากกว่าแรมปกติมาก ๆ ทว่า ในอนาคต SRAM จะกลายเป็นปัญหาในการผลิตชิปไปเสียแล้ว

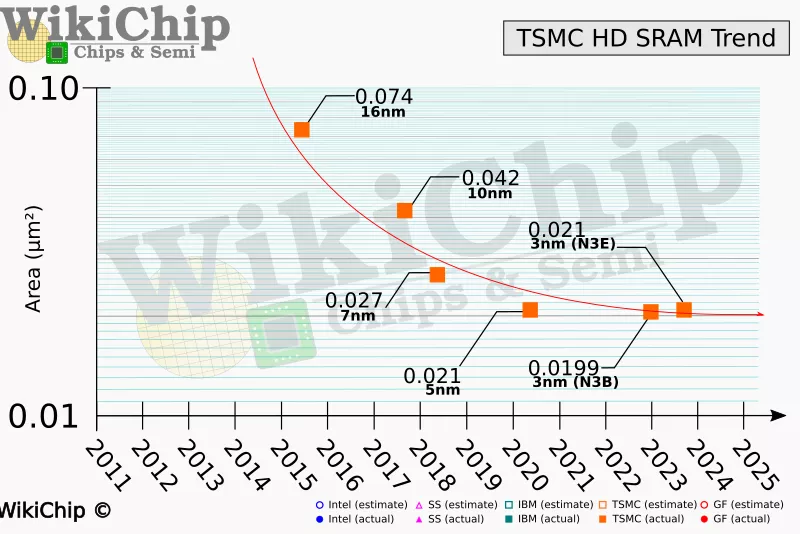

ในงานประชุม IEEE International EDM ครั้งที่ 68 ทาง TSMC เผยปัญหาใหญ่ในการพัฒนาชิปประมวลผล โดยพุ่งประเด็นไปที่ขนาดของ SRAM ซึ่งในช่วงปี 2020 เป็นต้นมา การลดขนาดของ SRAM เริ่มอยู่ในจุดอิ่มตัว และมันกำลังกลายเป็นปัญหาที่ต้องได้รับการแก้ไขโดยเร็ว

จะเห็นว่าในโหนดการผลิตทรานซิสเตอร์ 5nm, 3nm (N3B) และ 3nm (N3E) ขนาดของ SRAM แทบจะไม่ลดลงเลย ผิดกับยุค 16nm ลงมาถึง 7nm ที่ขนาดของ SRAM ลดลงสอดคล้องกับขนาดของทรานซิสเตอร์ที่ใช้เป็นแกนประมวลผลของซีพียู

ถามว่าทำไมมันถึงเป็นปัญหาขนาดนั้น? นั่นเป็นเพราะว่าขนาดของ SRAM บนชิปจะไปกินพื้นที่ของแกนประมวลผล ทั้งที่ผู้ผลิตควรได้พื้นที่สำหรับอัดทรานซิสเตอร์ของแกนประมวลผลซีพียูได้มากขึ้น ในขณัที่โหนดการผลิตกำลังลดลงเรื่อย ๆ แต่กลับต้องเสียพื้นที่ส่วนหนึ่งไปให้กับ SRAM จึงส่งผลให้ประสิทธิภาพที่ได้ไม่ดีเท่าที่ควร

นอกจากนี้ การที่ขนาดของ SRAM ไม่ลดลง ทำให้ขนาด Die ของชิปประมวลผลไม่ได้ลดลงตามที่ควรเป็น หมายความว่าปกติแล้วเราออกแบบทรานซิสเตอร์ด้วยโหมดการผลิตที่เล็กลง เพื่อให้จุทรานซิสเตอร์ได้มากขึ้น และเพื่อให้ชิปมีขนาดเล็กลง แต่ถ้า SRAM ยังมีขนาดใหญ่อยู่เช่นนี้ Die ของชิปประมวลผลก็ไม่อาจทำให้เล็กลงได้ตามที่คาดไว้

ซึ่งถ้าไม่สามารถลดขนาดของ SRAM ลงได้อีกแล้ว วิธีแก้ไขก็มีอยู่หลายรูปแบบ เราอาจออกแบบวิธีการจัดวางส่วนประกอบต่าง ๆ ภายในชิปเสียใหม่ เช่น การนำส่วนประกอบมาวางซ้อนกันแบบ 3D แต่ก็จะเพิ่มค่าใช้จ่ายในการพัฒนา หรืออาจเป็นการลดขนาดของ SRAM แต่ก็จะสิ่งผลต่อประสิทธิภาพซีพียู หรืออาจจะเปลี่ยนไปใช้หน่วยความจำแบบอื่นแทน SRAM เช่น MRAM, FeRAM และ NRAM เป็นต้น

ถึงกระนั้น หากไม่มีวิธีการใดที่เหมาะสม ทางผู้ผลิตชิปคงจะต้องพยายามลดขนาดของ SRAM ให้ได้ เพื่อให้ชิปประมวลผลในโหนดการผลิตขนาดเล็กลงสามารถแสดงศักยภาพออกมาได้ดีที่สุด

ขอขอบคุณข้อมูลจาก Techspot

You must be logged in to post a comment.